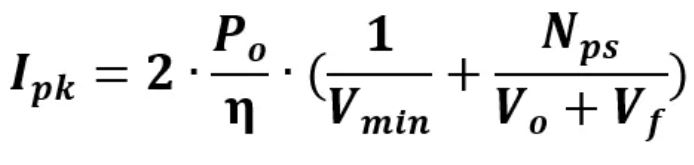

双管反激240W USB PD3.1 EPR设计要点

USB PD组织发布了最新的USB PD3.1 EPR规范,最大的输出达到48V5A, 240W的功率,使得传统的单开关QR Flyback方案难以满足设计指标,不管是开关管的峰值电流承受能力以及管子的电压应力还是效率都难以满足要求,而LLC拓扑结构虽然有着很高的效率但是又很难满足接近十倍的输出电压范围指标,如果LLC的后级再使用一级DC/DC变换器那么低压及轻载下的效率又会因为DC/DC的低指标而变得很差甚至不能满足COC及DOE的能效标准。

本文引用地址://www.cazqn.com/article/202405/458856.htm在此背景下,我们将介绍使用高频QR控制器NCP1345设计双管反激240W USB PD3.1 EPR方案。本文为第一部分,将重点介绍概述、变压器匝比要求、PFC在不同的输入电压下的开通和关断要求、变压器设计等。

概述

双管反激QR变换器架构很好地解决了前面提到的难题,双管反激QR变换器可以输出很宽的电压范围,通过合理的选择变压器匝比,可以使初级的双开关近似工作在ZVS开通,同时高匝比的应用也使得初级的电流减小,开关损耗和导通损耗得以减少,后级同步整流管可以使用常用的120V的MOSFET,降低了整体成本。

双钳位二极管又可以把漏感的能量回馈到输入端,消除了漏感能量损耗, 还有一个最大的优点就是相对其它软开关控制器, QR Flyback设计调试非常简单,对器件的要求相对较低,GaN的普及应用又能让开关频率提高并且低的谷底开通电压下的损耗非常小。

NCP1345是NCP1342的下一代升级版本,对多个功能进行改善更新,提供了双VCC端子,电压分别为38V和150V,改进了抖频模式来降低抖频带来的输出纹波,自适应的SKIP负载点确保不同的输出电压下进入SKIP的负载点相同来减小纹波电压,快速精确的初级OVP保护,初级恒流控制确保不同的输出电压下的OCP保护电流值相同,还有设定输出钳位电压用来直接驱动GaN,可设定的自适应驱动速度来降低次级应力等功能。

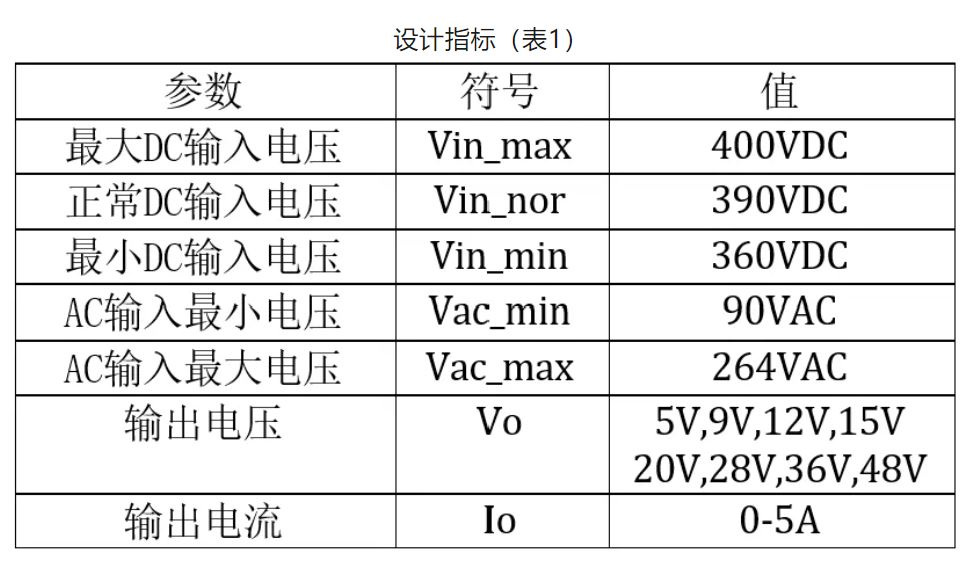

变压器匝比要求

双管QR Flyback架构由于是双开关串联工作,所以可以承受很高的反射电压N*Vo,高反射电压能让QR振荡的谷底接近零电压,可以做到近似零电压开通,如果反射等于或大于输入电压那就是完全的ZVS开通,但是双管QR Flyback拓扑结构由于双二极管钳位原因,要求变压器的反射电压N*Vo要小于最小的输入电压,否则反射电压会被输入电压钳位导致输出电压下降最终触发OLP保护,所以最大匝比N必须要限制。

理论上,双管反激变换器的Dmax=0.5, 实际上由于QR振铃的存在及谷底开通增大了Toff的时间,所以实际的Dmax<0.5。

对于输入电压,假定最小值为Vin_min=360V。在360V和48V5A的条件下Fmin=100KHz,T=10uS,QR振铃的频率为1MHz, 那么对于GaN开关管,1/2*TQR=0.5uS,参考图1Vds波形, 那么根据伏秒平衡,有下列方程:

PFC在不同的输入电压下的开通和关断要求

PFC的BULK电容量的最小值一般要求为输出功率的一半,所以BULK电容的容量选120uF,考虑到20%的容量误差那么电容的标称容量为150uF较为合适。

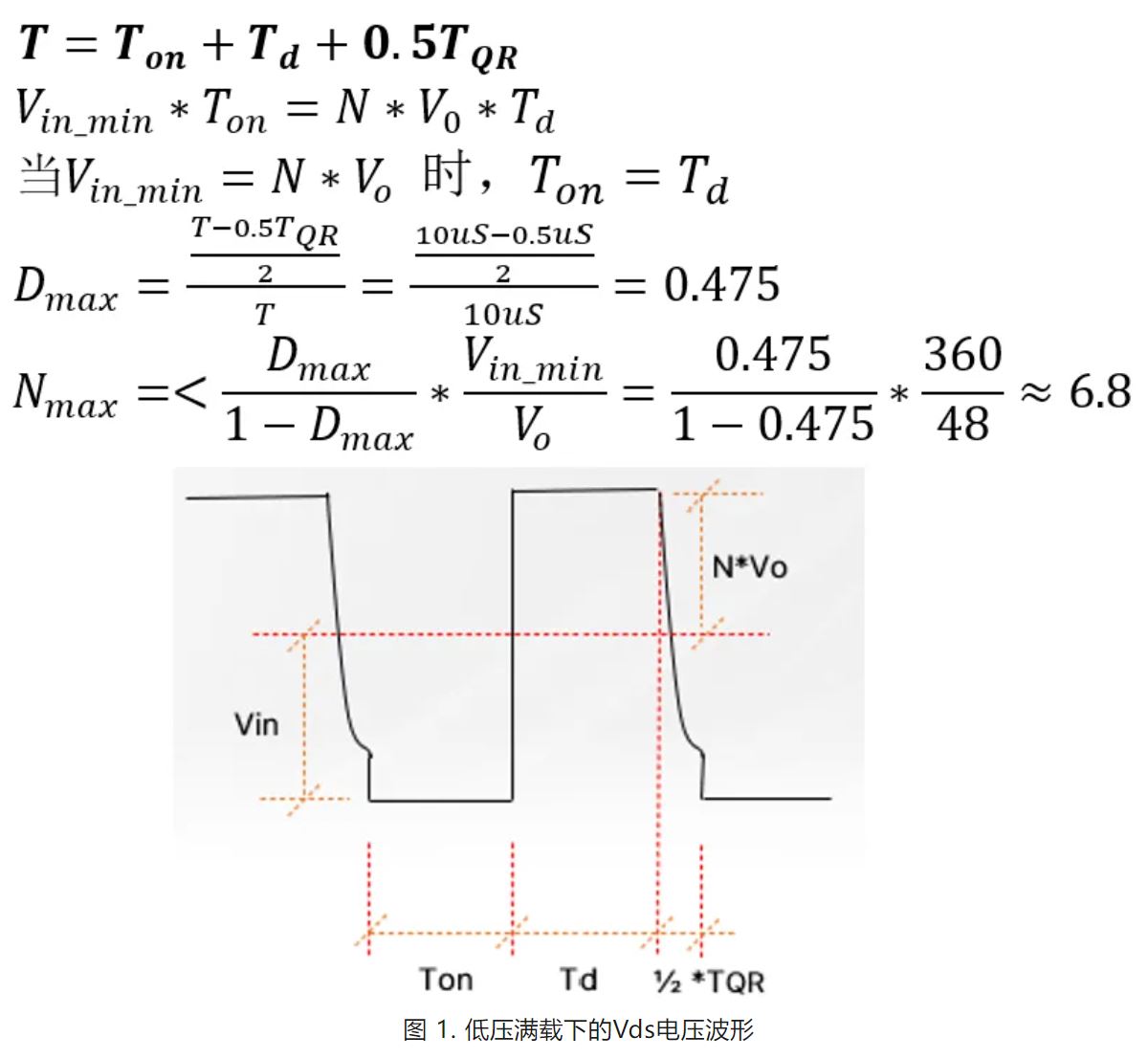

考虑到双管反激变换器对N*Vo的要求,需要计算90VAC下的滤波的直流电压的最低值来确定什么输出电压时可以关断PFC,这样可以确保在这个输出电压下BULK电容电压的最小值大于N*Vo。

图2是PFC停止工作下的AC输入电压对BULK电容电压充放电波形,根据能量平衡得到方程(1)

图 2. BULK电容电容充电放电波形 低压90VAC下的最低频率为57Hz, 所以TLINE=17.5mS,假定12V5A,15V5A下的效率为92%, BULK电容容量为120uF,那么根据方程(1),(2),(3),(4)计算得到: VBULKmin=94V @60W的功率 根据前面估算的匝比N=6.8, 那么12V输出变压器反射电压为:Vor=12V*6.8=81.6V 15V时输出时变压器反射电压为:Vor=15V*6.8=102V 所以PFC必须要在12V和15V之间关断来确保Vor要小于BULK电容电压的最低值94V.实际应用中可以让PD协议控制器把PFC的ON/OFF时的电压设定在12V-12.5V左右并留有一个小的回差电压防止PFC在ON和OFF之间来回开关, 这样BULK电压最小值比Vor大9V左右且留有足够的余量。 根据上面的计算,可以把PFC ON的输出电压设置在12V-12.5V左右来确保PFC OFF条件下在5V-12V输出时双管Flyback还能可靠地工作,同时又能提高整机效率并且降低待机功耗。

变压器设计

条件:

输出功率Po=240W

输出电压Vo=48V

估算效率η=0.95

最小输入电压Vmin=350V(留10V余量)

变压器匝比N=6.8, Nps=Ns/Np=0.147

同步整流管的压降Vf=0.1V

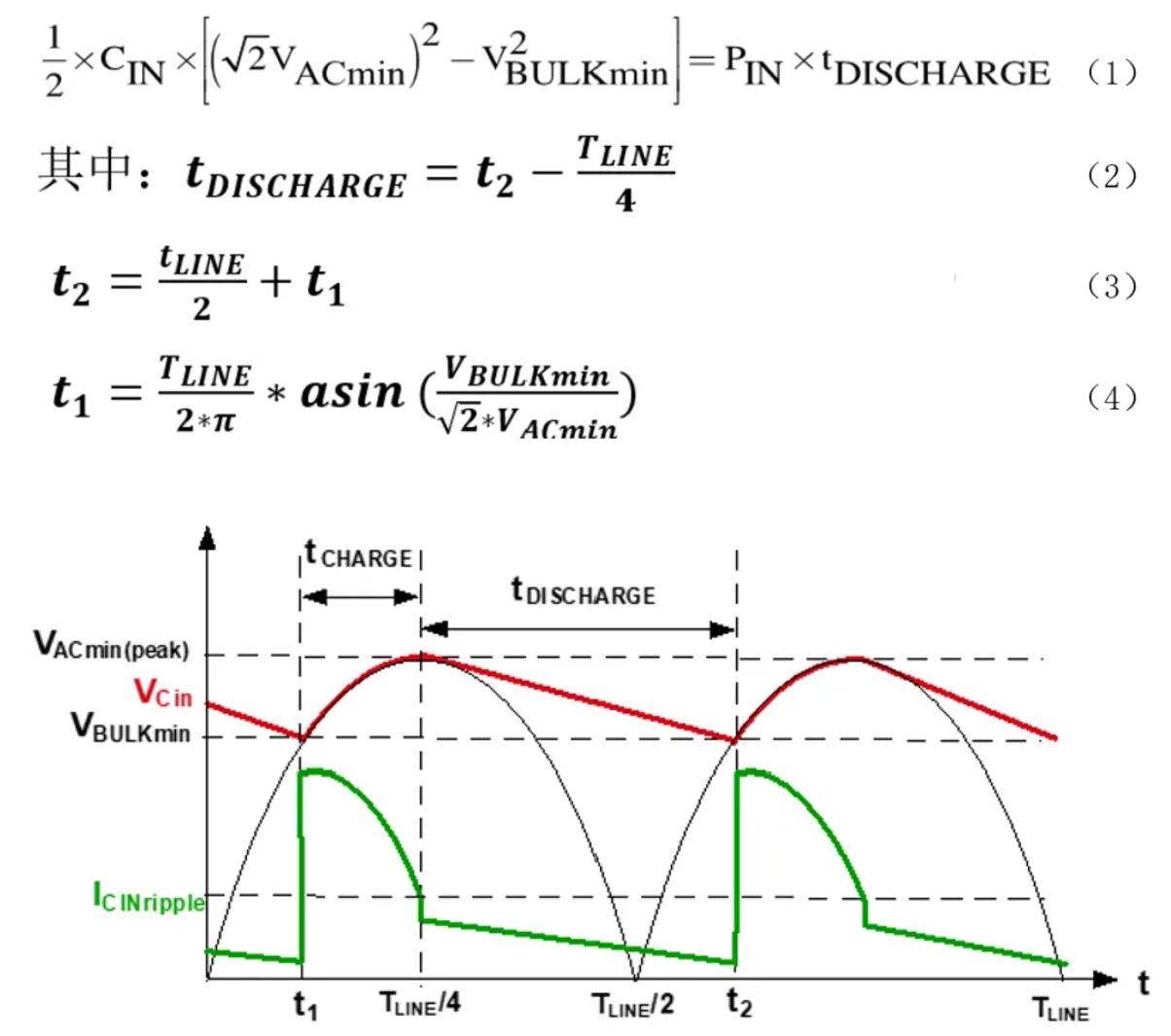

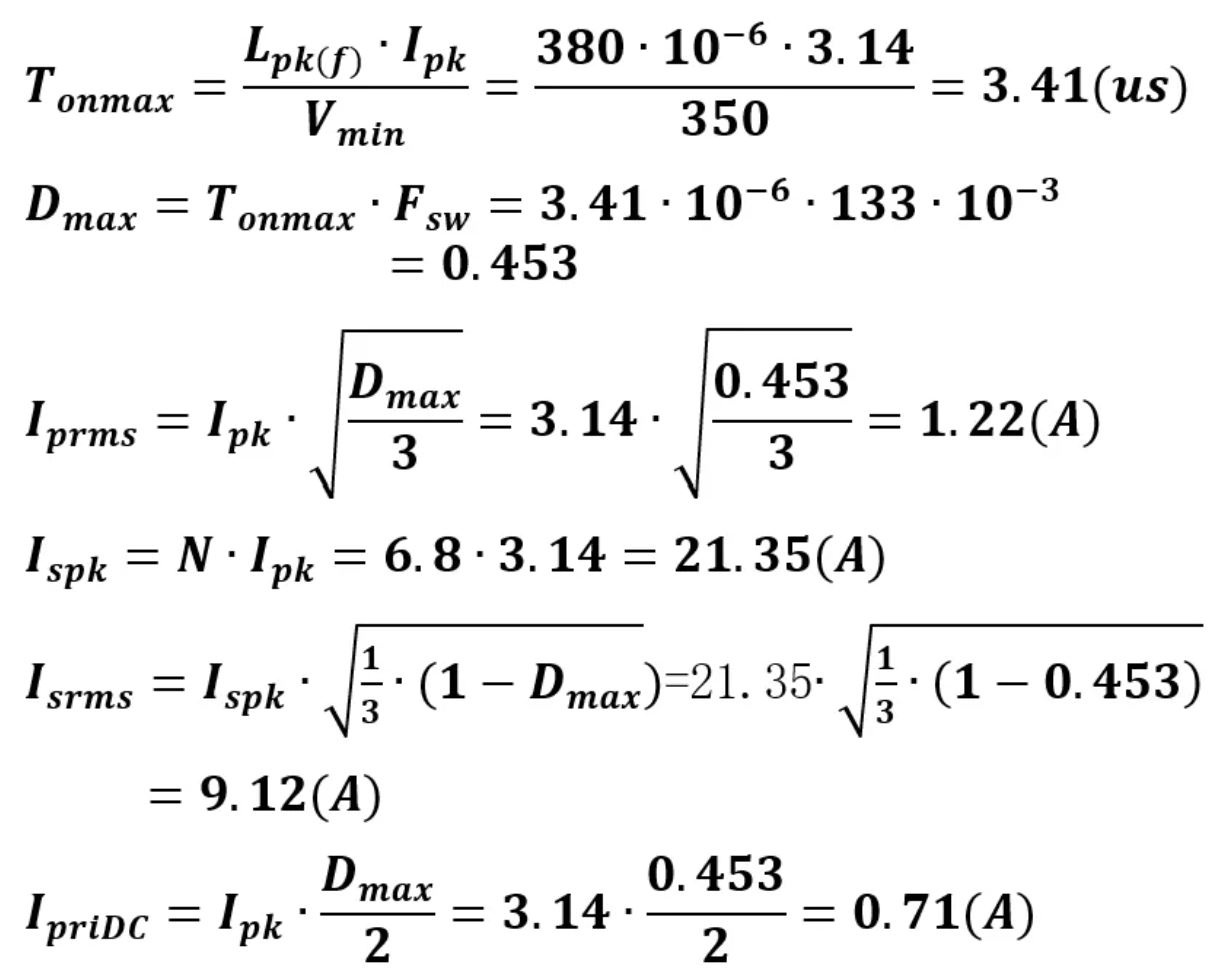

首次计算由于不知道电感量是多少,所以无法估算QR振铃的周期,忽略QR振铃的半周期死区时间,得到如下初级峰值电流方程:

计算得到:Ipk≈3A

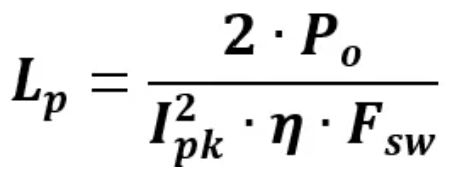

变压器电感量方程:

假定Fsw=133KHz, 计算得到:

Lp=430uH

查DrvGaN NCP58922的规格书得到Coss=35pF

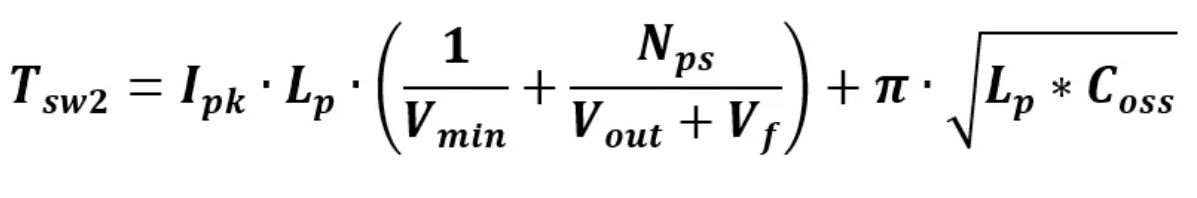

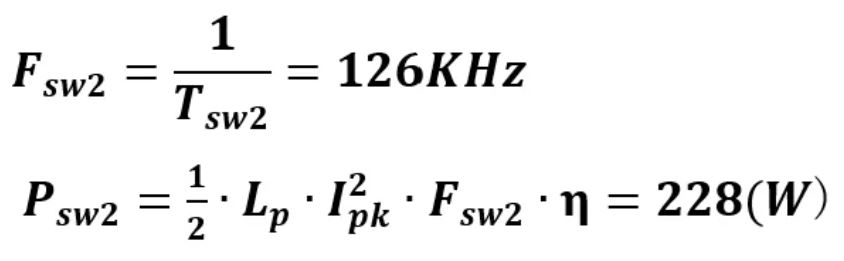

再考虑QR振铃的半周期死区时间,得到如下周期频率及输出功率计算方程:

代入首次计算得到的电感量Lp及Coss值,计算出开关频率及输入功率如下,可以看出开关频率和原始设定的频率相比偏低,对于同样的峰值电流,输入功率也比原始定义的偏小, 原因是开始不知道变压器的电感量的大致范围,所以第一次计算峰值电流的时候没有加入QR振铃导致的死区时间。

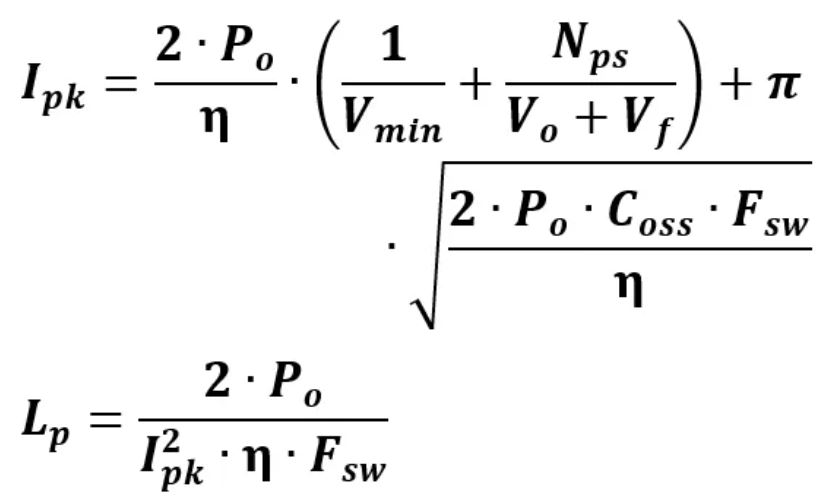

包含了QR振铃死区时间的峰值电流及电感的方程:

重新计算得到:

Ipk=3.14A

Lp=386μH

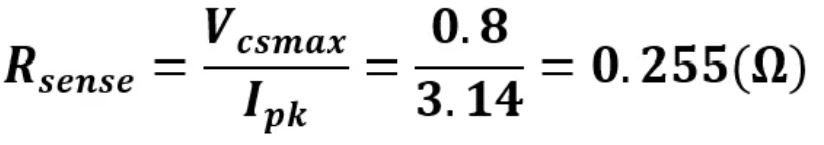

考虑到NCP1345的初级恒流值,最终Rsense取值:

Rsense(f)=0.39Ω//0.36Ω=0.187Ω

取Lp(f)=380μH

变压器匝数计算:

变压器磁芯用PQ3218, Ae=169mm²

极端情况下变压器最大的峰值电流

校验匝比N符合最大匝比要求

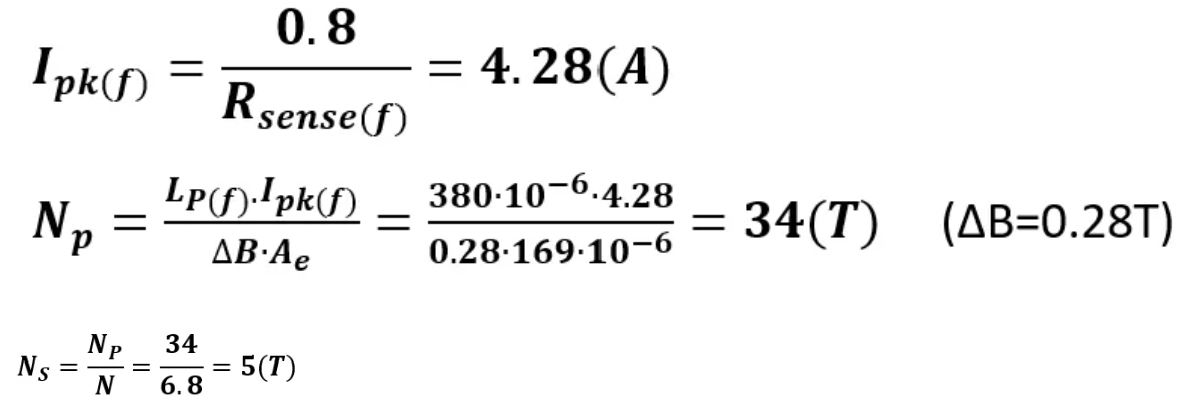

根据最终确定的电感量及频率来计算Dmax和N是否在最大允许范围内。

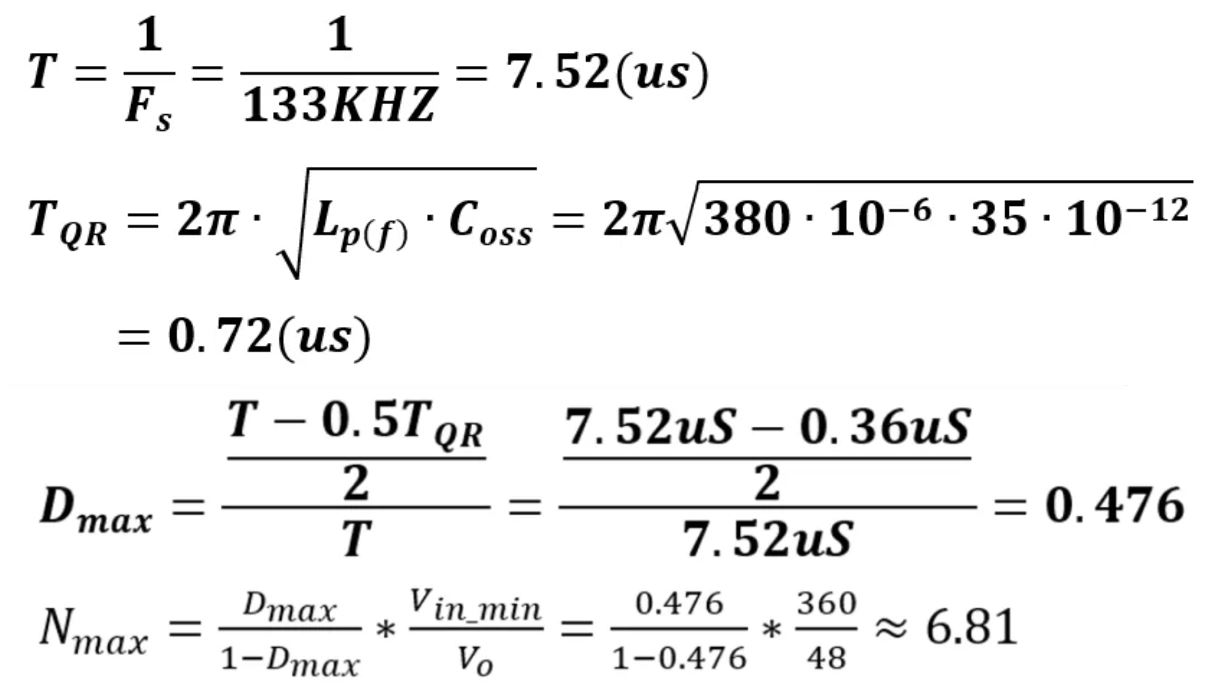

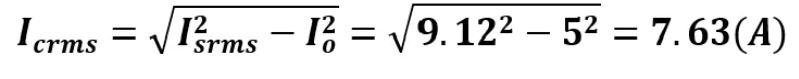

结论:实际匝比N满足最大限制要求 额定条件下初级和次级RMS电流及初级电流平均值

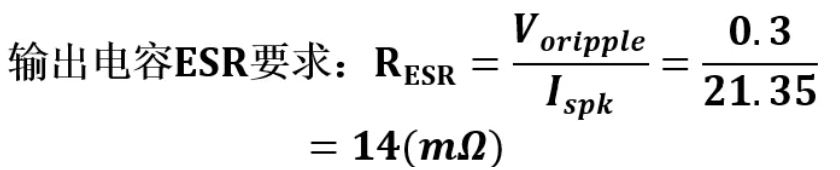

输出电容

假定输出允许纹波电压Voripple=0.3V

输出电容电流有效值要求:

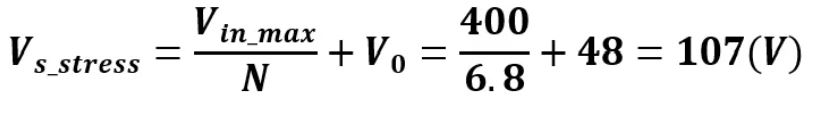

初次级开关管电压应力

初级由于是双管串联工作,所以电压应力不是问题。

次级应力:

NCP1345是QR谷底开通,所以在谷底开通时的次级应力很低,当第六个谷底后开通,开通时的电压升高,所以次级应力相对升高。IC可以设定在第三个谷底及以后的开通具有非常慢的开通速度来降低次级应力,选用120V的同步MOS,实测在48V0.5A时最高次级应力大约113V,大约6%的应力余量。

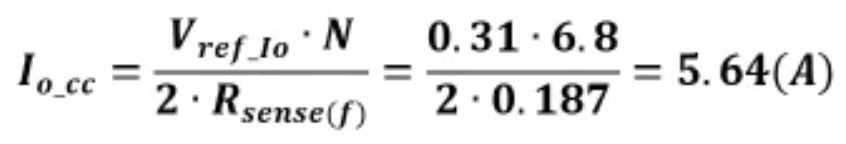

NCP1345初级恒流值

NCP1345提供初级控制次级恒流输出,这种恒流值在任意输出电压下都是相同的,所以对于PD的应用提供了非常好的OCP保护。如果是普通的控制器仅仅靠峰值电流来做OCP,那么在低压输出的情况下OCP保护点将会非常大,根本没有保护作用。

输出恒流值为:

其中Vref_Io为NCP1345Q01内部设置的恒流参考常数,从这个结果可以看出为什么当初选择Rsense的值为何减少那么多,主要是考虑到了恒流设定值。当然IC内部的恒流参考值还可以通过编程选择不同的值来满足不同的设计要求,这个Rsense选择主要是考虑到直接可以用NCP1345Q01这颗已有的型号。

NCP1345 ZCD脚功能

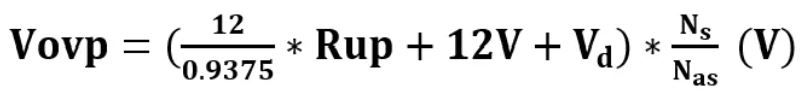

NCP1345通过ZCD脚感应辅助绕组电流过零点的电压并通过电阻分压然后输入的ZCD脚,去磁电流过零点检查输出电压消除了后级同步管压降对输出电压的影响,让内部的电压比较器提供精确快速的OVP保护,提供了小于一个周期的OVP保护响应速度,波形及外部电路如图3所示。

ZCD脚除了提供OVP功能外,还作为去磁电流过零及谷底检测,实现QR谷底开通,同时时还作为OPP补偿设定。在开机时Pre-Startup开关接通,QR Enable开关断开,Iopp电流源流过Ropp电阻后产生的电压被内部检测做为高低压下OPP过流保护点的补偿。在这个设计中由于15V以上输出电压时PFC电路都是工作的,所以输入电压变化很小几乎恒定,OPP功能没有被使用,只要将Ropp阻值设置在15K就可以屏蔽OPP补偿功能。

当OPP检测完成后Pre-Startup开关断开,QR Enable开关接通,Ropp电阻和内部1K的下拉电阻并联,和Rup电阻组成分压电路,分压的Vzcd供ZCD电流过零及谷底检测,同时提供给OVP电路,OVP比较强的参考电压为12V。ZCD检测具有非常宽的电压范围,从大约0.1V到12V都没问题,所以根据OVP保护设置的外部分压电阻自然可以适应ZCD检测。

OVP电压设置:

Vovp: 设计的输出电压保护值

Rup: 分压电路的上部电阻

Ns: 次级绕组匝数

Nas: 初级辅助绕组匝数

Vd: 二极管D的正向压降为0.6V

文章来源:安森美

评论