2022 年 12 月 22日,纽约州罗彻斯特 – Keypoint Intelligence 将Buyers Lab (BLI) 2023 年度精选奖授予 Kodak Alaris 的Kodak S3140 Max 扫描仪。BLI 精选奖旨在表彰过去六个月在 Keypoint Intelligence 实验室的广泛测试中表现优异的办公技术产品。2022 年 5 月推出的 S3140 Max 扫描仪兼具大容量和台式机的简易操作性及紧凑结构。该生产式扫描仪非常适合多文档流程,可提供杰出的影像质量、卓越的纸张

关键字:

Kodak Alaris Keypoint Intelligence BLI 2023 年度精选奖

最大的自动自主系统软件框架提供商RTI公司宣布将于2023年1月5-8日在拉斯维加斯参展CES 2003,展示支持软件定义汽车且已获安全认证的车规级互连框架Connext Drive®。这是一套以数据为中心的集成化敏捷框架,可确保软件堆栈的灵活性,支持软件架构师把智能互连机制从硬件和操作系统中抽象出来,将其置于汽车的核心。在CES展台上,RTI公司将采用众多领先的硬件和软件平台,针对下一代汽车开发中的重大挑战,整合进行三项演示:以区域为导向(Zonal)的架构、高性能计算和车载娱乐系统/云互连。这三个展示

关键字:

RTI公司 CES 2023 软件定义车辆互连框架 Connext Drive

Analog Devices, Inc.诚邀公众和媒体参与CES 2023,期待通过演示互动和专家研讨,一同感受边缘智能带来的别样生活体验。参观ADI展位:通过边缘感知和数据处理技术连接现实世界和数字世界,令数据和见解更贴近决策端,从而提高执行速度和效率。欢迎大家前往ADI位于拉斯维加斯会议中心西大厅的4725号展位,了解ADI智能边缘技术如何时刻影响我们生活的方方面面,并通过实现更高效、更安全和可持续的未来,应对全球面临的诸多重大挑战。“边缘洞察”主题座谈:ADI高管将联合专家和思想领袖,共同展开一系列

关键字:

ADI CES 2023

§ 各规模企业均遭受攻击风险,其中由恶意软件造成的事件占CyberSOC(检测和响应运营中心)总量的40%;§ 99,000多起调查显示,安全事件数量同比增长5%,每个客户平均每月发生34起安全事件,每个组织每天至少发生1起安全事件;§ 从2021年到2022年,网络勒索受害者的所在地发生了显著变化,其中北美的受害者数量有所减少(美国-8%、加拿大-32%),但欧洲(+18%)、英国(+21%)、北欧(+138%)和东亚(+44%)的受害者数量有所增加;§&

关键字:

网络安全服务供应商Orange Cyberdefense Security Navigator 2023

自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,近日于北京宣布,针对面向专业音频/视频(Pro AV)和广播市场的赛灵思器件推出一系列全新的高级机器学习(ML)功能。此外,赛灵思还演示了业界首个基于7nm Versal™ 器件的可编程 HDMI 2.1 实现方案。赛灵思将在本周于阿姆斯特丹举办的 2020 年欧洲集成系统展( ISE )上展出这些功能和更多其他功能。上述解决方案以及赛灵思面向 Pro AV 和广播市场推出的其他高度自适应解决方案,旨在帮助客户降低成本、适应未来,同时适应

关键字:

ML ISE

国际研究暨顾问机构Gartner预测,未来三年户外监视摄影机将成为全球5G物联网(IoT)解决方案最大市场,在2020年时达到5G物联网端点装机总数70%。就数量而言,2020、2021和2022年将分别为250万、620万和1,120万台,不过到了2023年时将被联网汽车超越,萎缩至市场的32%。

关键字:

联网汽车 2023 5G

FPGA实战开发技巧(4)-在代码编写完毕后,需要借助于测试平台来验证所设计的模块是否满足要求。ISE 提供了两种测试平台的建立方法,一种是使用HDL Bencher 的图形化波形编辑功能编写,另一种就是利用HDL 语言,相对于前者使用简单、功能强大。

关键字:

FPGA ISE

如何在EDK中使用自己的 IP核?-如何在EDK中使用自己的 IP核呢? 这是很多人梦寐以求的事情。然而在EDK以及ISE的各种文档中对此却遮遮掩掩,欲语还休。

关键字:

赛灵思 ISE IP

介绍一种基于FPGA的精密离心机光栅信号细分系统。说明了光栅信号的产生过程和基本处理方法,提出了一种综合EDA技术与光栅莫尔条纹电子学细分技术的设计方案。通过VerilogHDL实现该系统的主要设计,并利用ISE软件进行了仿真试验。试验表明,该系统具有捕捉速度快、跟踪精度高、相位误差小、成本低廉等特点。

关键字:

ISE 信号细分系统 光栅信号 FPGA

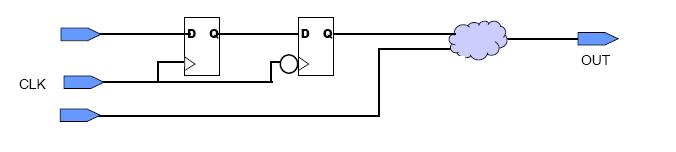

时钟上升沿和下降沿之间的时序约束

周期约束可以自动计算两个沿的的约束——包括调整非50%占空比的时钟。

例:一个CLK时钟周期约束为10ns,能够应用5ns的约束到两个寄存器之间。

不需要特定路径应用到这个例子中。

相关时钟域的约束

为一个时钟进行周期约束——以这个周期约束确定相关的时钟。

执行工具将根据它们的关系来决定如何处理跨时钟域。

DCM有多个输出:

—&md

关键字:

ISE 时序约束

回顾全局OFFSET约束

在时钟行中使用Pad-to-Setup和Clock-to-Pad列为所有出于该时钟域的I/O路径指定OFFSETs。

为大多数I/O路径进行约束的最简单方法——然而,这将会导致一个过约束的设计。

指定管脚的OFFSET约束

使用Pad-to-Setup和Clock-to-Pad列为每个I/O路径指定OFFSETs。

这种约束方法适用于只有少数管脚需要不同的时序约束。

更常用的方法是:

1. 为Pads生成Gro

关键字:

ISE 时序约束

特定路径时序约束

使用全局时序约束(PERIOD,OFFSET,PAD-TO-PDA)将约束整个设计

仅仅使用全局约束通常会导致过约束

——约束过紧

——编译时间延长并且可能阻止实现时序目标

——通过综合工具或者映射后时序报告重新审视性能评估

特定路径约束能够覆盖全局时序约束在特定路径上的约束

——这就允许设计者放宽特定路径的时序要求

更多关于特定路径约束

关键字:

ISE 时序约束

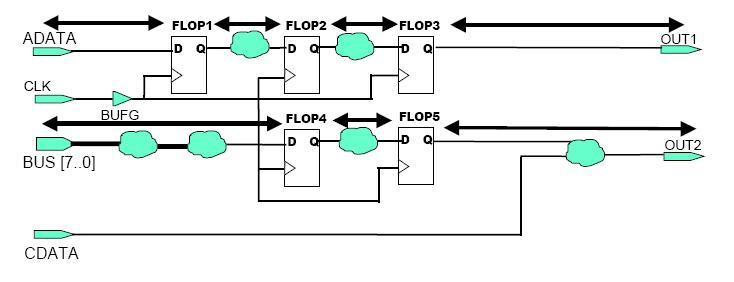

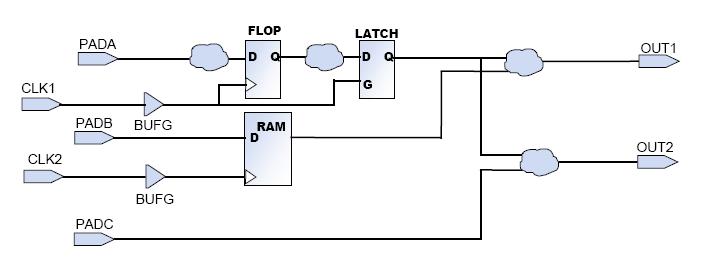

问题思考

在这个电路中哪些路径是由OFFSET IN 和 OFFSET OUT来约束的?

问题解答:

——OFFSET IN:PADA to FLOP and PADB to RAM

——OFFSET OUT:LATCH to OUT1, LATCH to OUT2, and RAM to OUT1

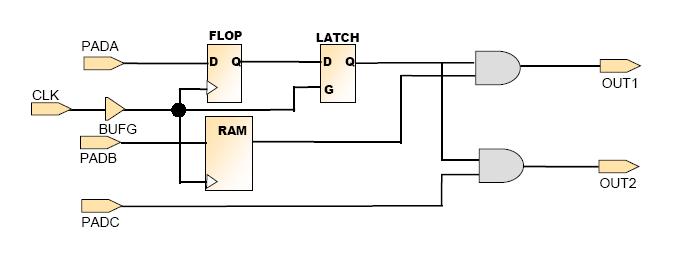

问题思考

下面给出的系统框图里,你将给出什么样的约束值以使系统能够跑到100MHz?

关键字:

ISE 时序约束

问题思考

哪些路径是由CLK1进行周期约束?

哪些路径是由pad-to-pad进行约束?

OFFSET约束

OFFSET约束覆盖以下路径:

——从input pads到同步单元(OFFSET IN)

——从同步单元到output pads(OFFSET OUT)

OFFSET约束特性

OFFSET约束自动计算时钟分布延时

1. 提供最准确的时序信

关键字:

ISE 时序约束

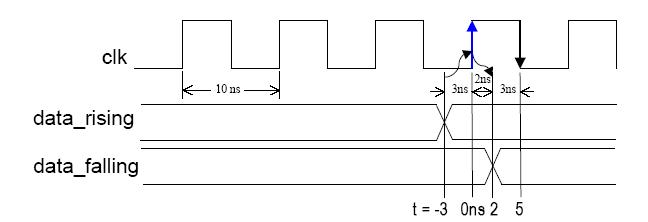

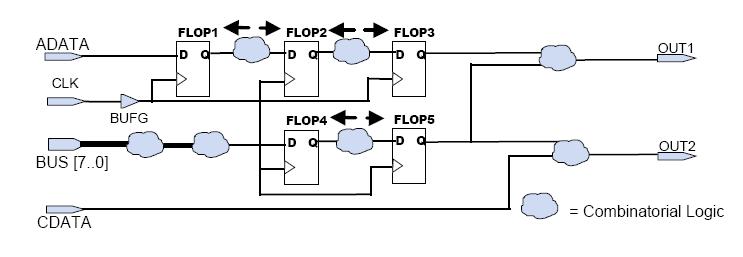

问题思考

单一的全局约束可以覆盖多延时路径

如果箭头是待约束路径,那么什么是路径终点呢?

所有的寄存器是否有一些共同点呢?

问题解答

什么是路径终点呢?

——FLOP1,FLOP2,FLOP3,FLOP4,FLOP5。

所有的寄存器是否有一些共同点呢?

——它们共享一个时钟信号,约束这个网络的时序可以同时覆盖约束这些相关寄存器间的延时路径。

周期约束

周期约束覆盖由参

关键字:

ISE 寄存器

ise 2023介绍

您好,目前还没有人创建词条ise 2023!

欢迎您创建该词条,阐述对ise 2023的理解,并与今后在此搜索ise 2023的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

官方威廉希尔备用网址

-

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

威廉希尔 官网app

杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473